# SHARP

New Satellite W1Ø

PROGRAMMABLE CONTROLLER

User's Manual - 2

**SHARP CORPORATION**

## Contents

|              | User's                                   | Manual<br>Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2 |

|--------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 9-2          | Bit processing                           | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|              | Description of basic instructions        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

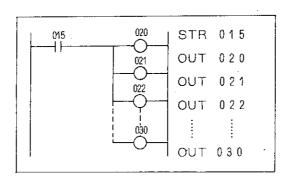

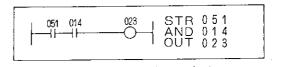

| [1]          | STR/OUT                                  | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

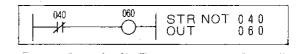

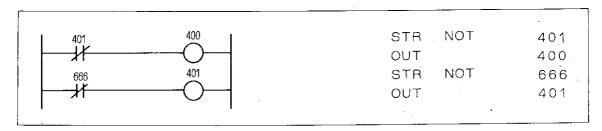

| [2]          | STR NOT                                  | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

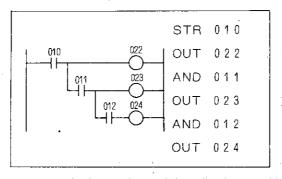

| [3]          | AND                                      | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

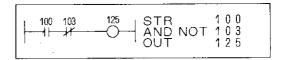

| [4]          | AND NOT                                  | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| [5]          | OR                                       | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| [6]          | OR NOT                                   | 111.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

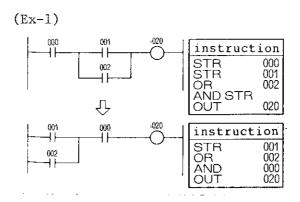

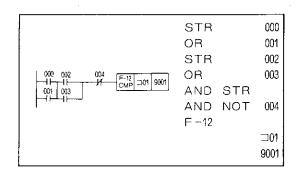

| [7]          | AND STR                                  | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

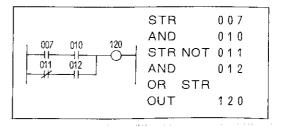

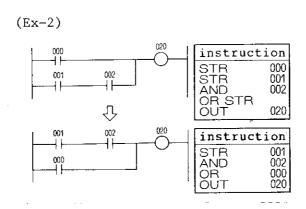

| [8]          | OR STR                                   | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

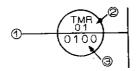

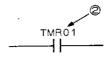

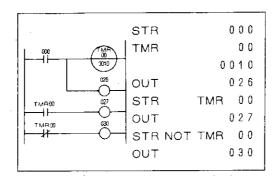

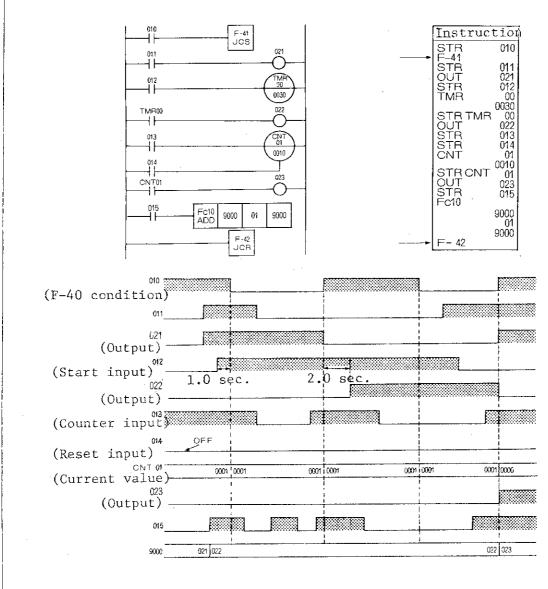

| [9]          | TMR                                      | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

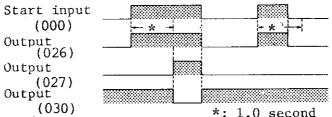

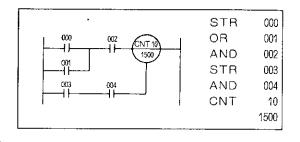

| [10]         | CNT                                      | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| 9-4          | Ladder design cautionary notes           | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - |

| [1]          | Relay circuit that needs revision        | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

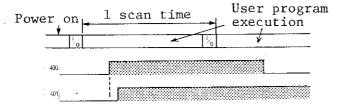

| [2]          | Input and output batch processing        | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| [3]          | Influence by the sequence of programming | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| [4]          | -                                        | - 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

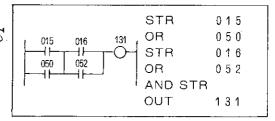

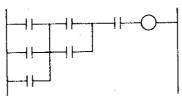

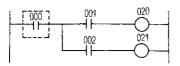

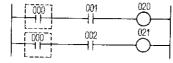

| [5]          | Programming serial/parallel circuit      | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|              | Application instruction cautionary notes | - 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

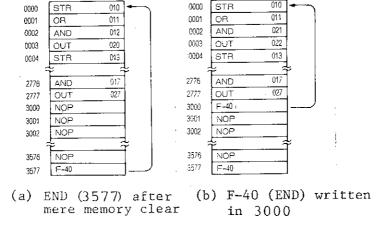

| 9-3<br>[1]   |                                          | - 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| [2]          |                                          | - 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| [3]          | and attack register                      | - 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| [4]          |                                          | - 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| [5]          | 1 53                                     | - 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| [6]          |                                          | - 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| [7]          |                                          | - 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|              | Description of application instruction   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| <i>J</i> , 0 | F-00 Transfer one byte data              | - 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

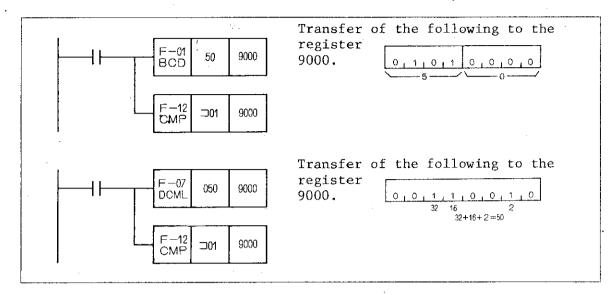

|              | F-01 Transfer BCD constant               | - 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

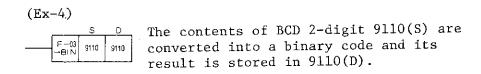

|              | F-03 Convert BCD into binary             | the state of the s |   |

|              | n 0/ Convert hipary into RCD             | - 153°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

|              | F-07 Transfer decimal constant           | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|     |             |                                               | Pag   |

|-----|-------------|-----------------------------------------------|-------|

| •   | F-08        | Transfer octal constant                       | 159   |

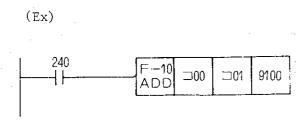

|     | F-10        | Add registers (BCD 2-digit)                   | * *** |

|     | Fc10        | Add register with 2-digit BCD constant        | 15    |

|     | F-11        | Subtract register by register in BCD 2 digits | 16    |

|     | Fcll        | Subtract register by 2-digit BCD constant     | 16    |

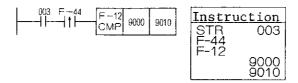

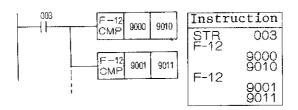

|     | F-12        | Compare registers                             | 16    |

|     | Fc12        | Compare register with constant                | 16    |

|     | F-13        | AND registers                                 |       |

|     | Fc13        | AND register with constant                    | 16    |

|     | F-14        | OR registers                                  | 16    |

|     | Fc14        | OR register with constant                     | 170   |

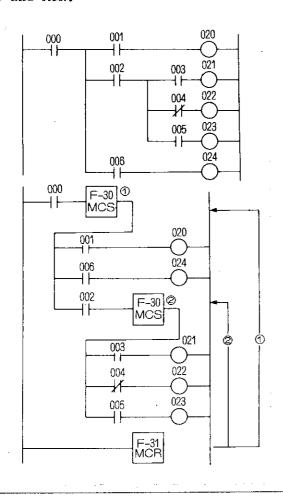

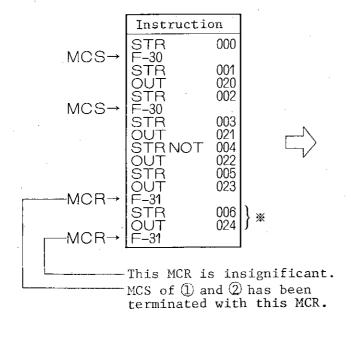

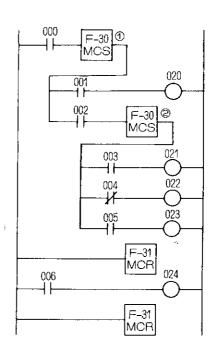

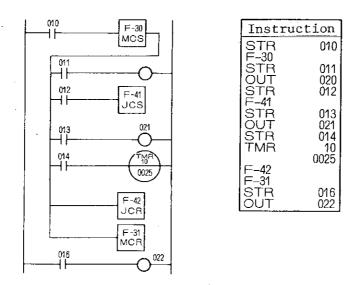

|     | F-30        | Set master control                            | 17    |

| ·   | F-31        | Reset master control                          | 17    |

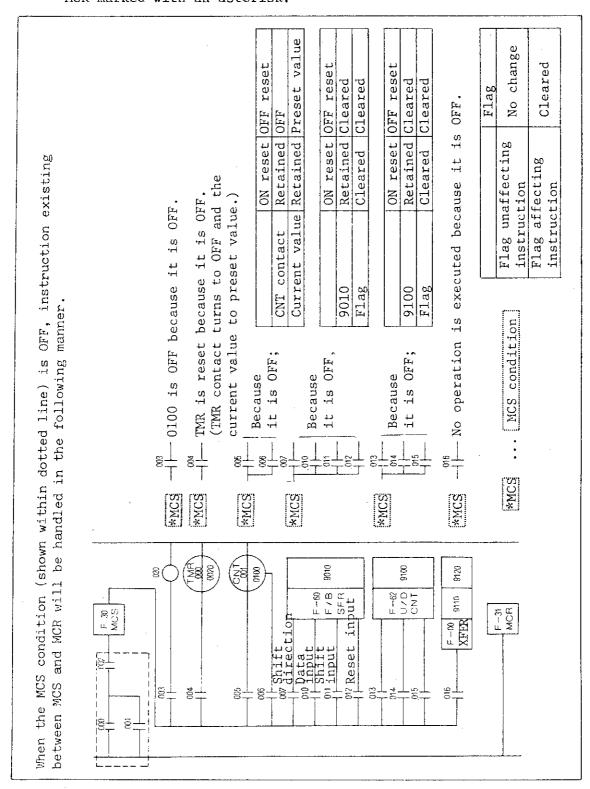

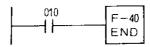

|     | F-40        | End instruction                               | 17    |

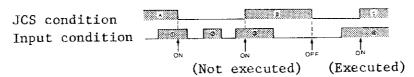

|     | F-41        | Set jump control                              | 17    |

|     | F-42        | Reset jump control                            | 17    |

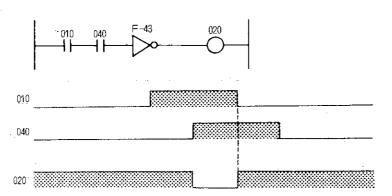

|     | F-43        | Complement bit                                | 180   |

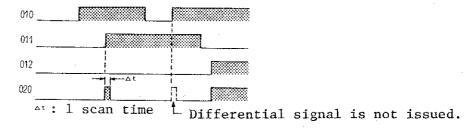

|     | F-44        | Differentiate at ON                           | 18    |

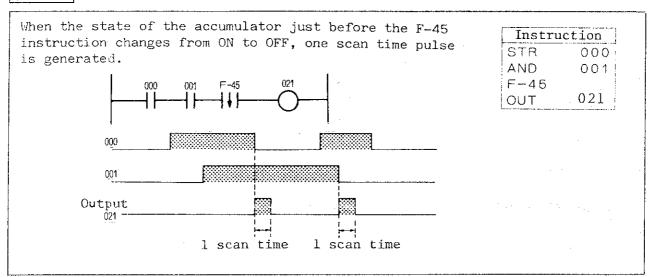

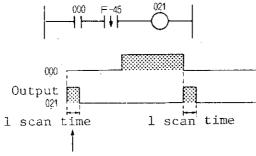

| . , | F-45        | Differentiate at OFF                          | 183   |

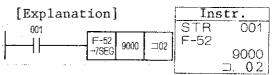

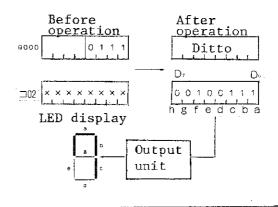

| !   | F-52        | Decode to 7-segment data                      | 18    |

|     | F-55        | Swap high order 4 bits with low order 4 bits  | 18    |

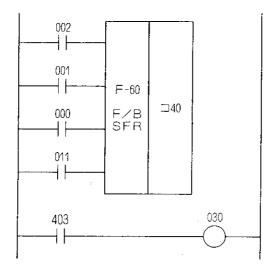

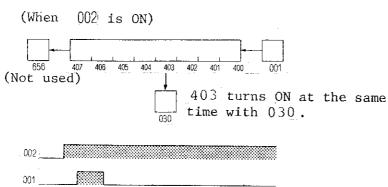

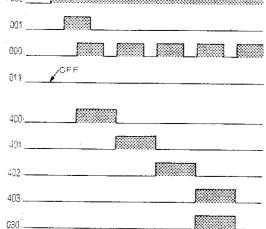

|     | F-60        | Shift register bidirectional                  | 18    |

| £   | F-62        | Set up/down counter                           | 19    |

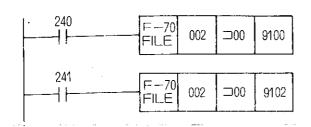

| •   | F-70        | Transfer n-byte in batch                      | 19    |

|     | F-71        | Transfer octal constant in batch              | 19    |

|     | <b>§</b> 10 | How to use support tools                      | 19!   |

|     | 1           | O-l programmer (ZW-lOPGl)                     | 195   |

| ,   | 1           | 0-2 Ladder Processor (Z-100LP1)               | 198   |

|     | 1           | 0-3 Ladder Processor II (Z-100LP2)            | 199   |

|     | 1           | 0-4 CF Loader (ZW-100CF1)                     | 200   |

£1. 1

|        |                                                            | Page |

|--------|------------------------------------------------------------|------|

| 11-1 F | Basic instruction applied circuit                          | 203  |

| [1]    | Ever-on circuit                                            | 203  |

| [2]    | Circuit from which a single pulse is generated at power on | 203  |

| [3]    | Oscillation circuit                                        | 204  |

| [4]    | Rise edge differentiation                                  |      |

| [5]    | Fall edge differentiation                                  | 207  |

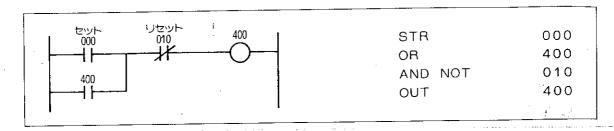

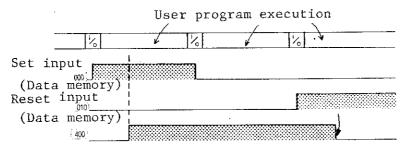

| [6]    | Self-hold circuit (with reset in priority )                | 207  |

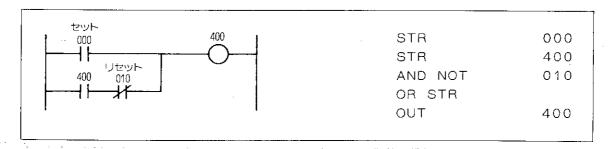

| [7]    | Self-hold circuit (with set in priority)                   | 208  |

| [8]    | Priority circuit                                           | 209  |

| [9]    | Alternate circuit                                          |      |

| [10]   | n-bit shift register                                       |      |

| 11-2   | Timer application circuit                                  |      |

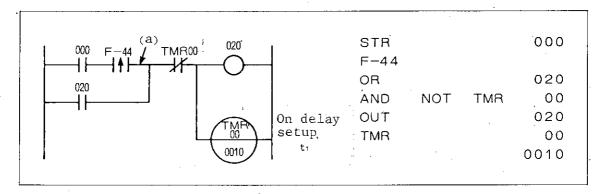

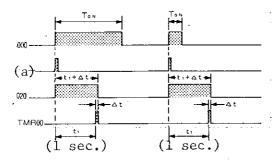

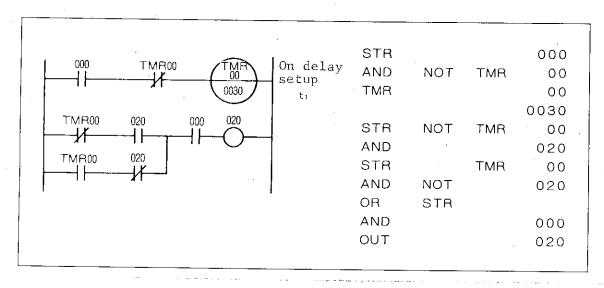

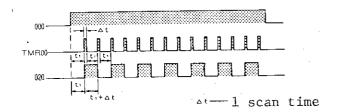

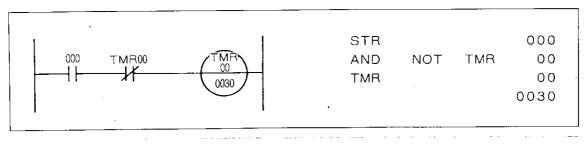

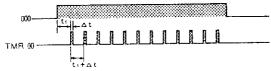

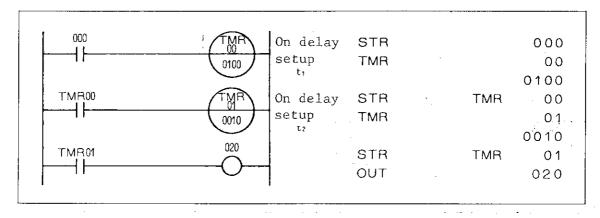

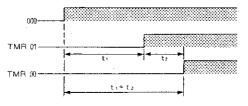

| [1]    | On delay timer                                             |      |

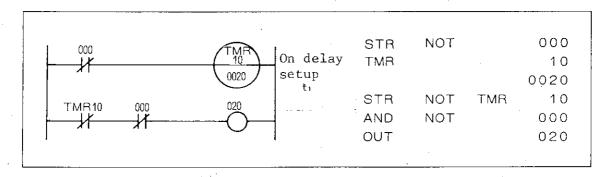

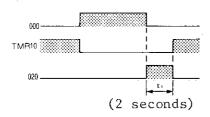

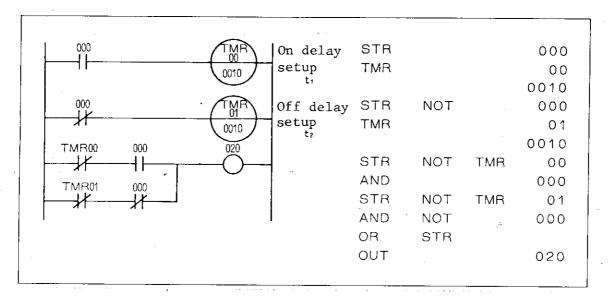

| [2]    | Off delay timer                                            | 213  |

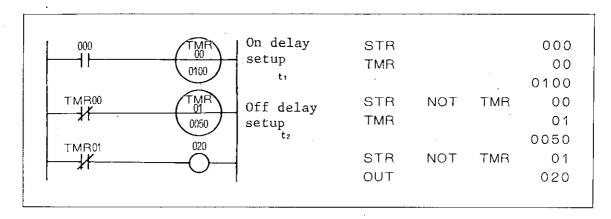

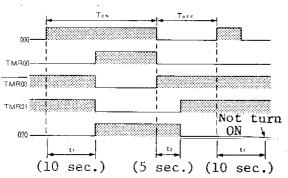

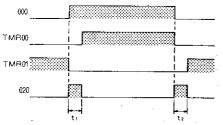

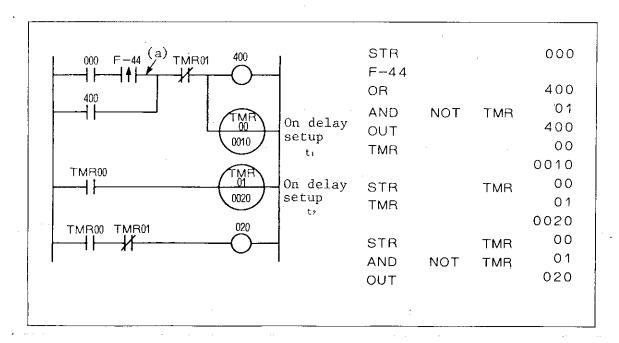

| [3]    | On/off delay timer                                         | 214  |

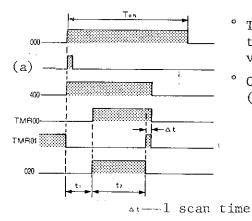

| [4]    | One shot timer at the input rise edge (1)                  |      |

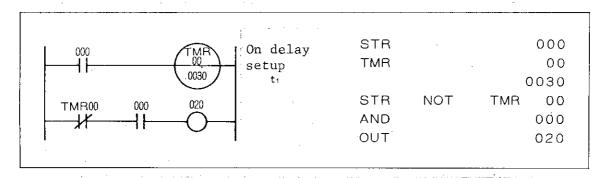

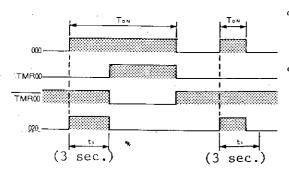

| [5]    | One shot timer at the input rise edge (2)                  |      |

| [6]    | One shot timer at the input fall edge                      | 215  |

| [7]    | One shot timer at rise/fall edge                           | 216  |

| [8]    | On delay one shot timer                                    | 217  |

| [9]    | Equispace pulse generation circuit                         | 217  |

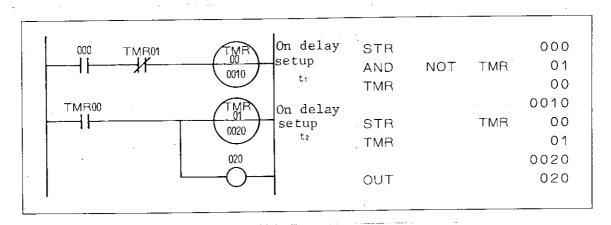

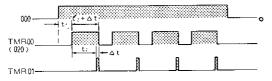

| [10]   | Duty variable pulse generator circuit (1)                  | 218  |

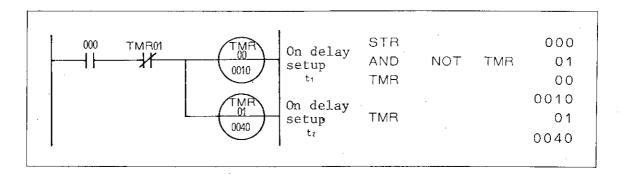

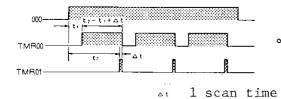

| [11]   | Duty variable pulse generator circuit (2)                  | 219  |

| [12]   | Long time timer (1)                                        | 219  |

| [13]   | Long time timer (2)                                        |      |

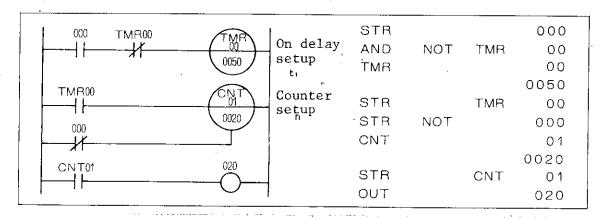

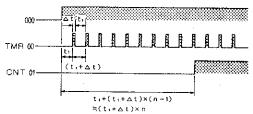

| 11-3   | Counter applications                                       | 220  |

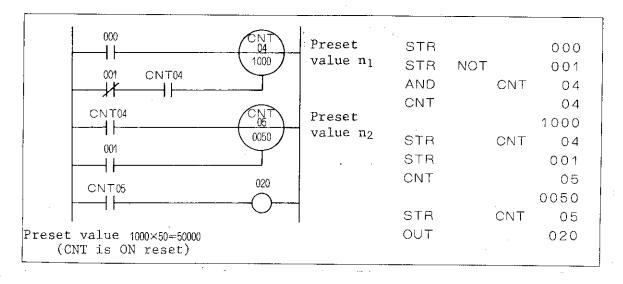

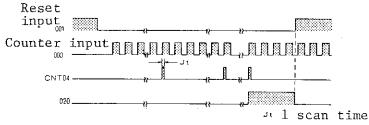

| [1]    | Large capacity counter (1)                                 | 220  |

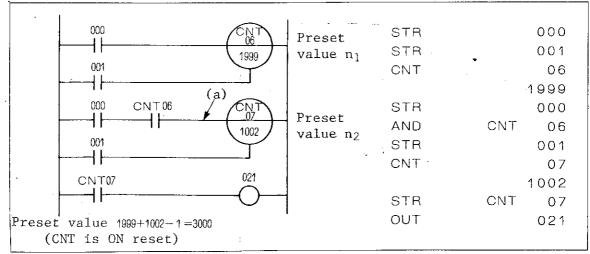

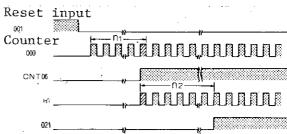

| [2]_   | Large capacity counter (2)                                 | 221  |

| 11-4 I | Data processing instruction applications                   |      |

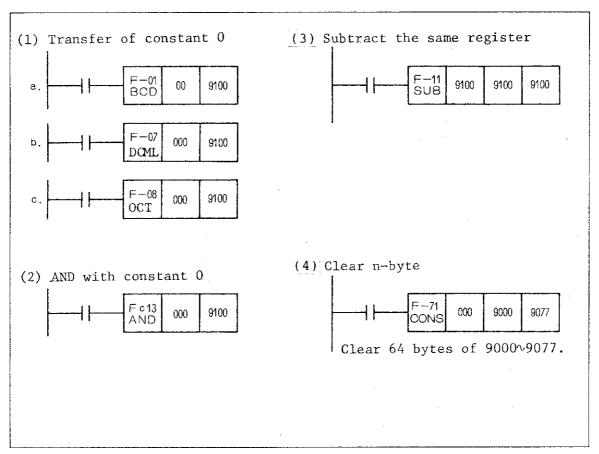

| [1]    | Register clear                                             |      |

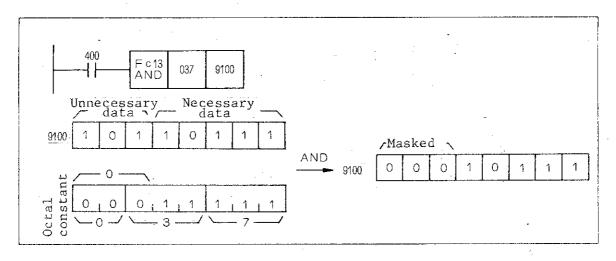

| [2]    | Masking data                                               |      |

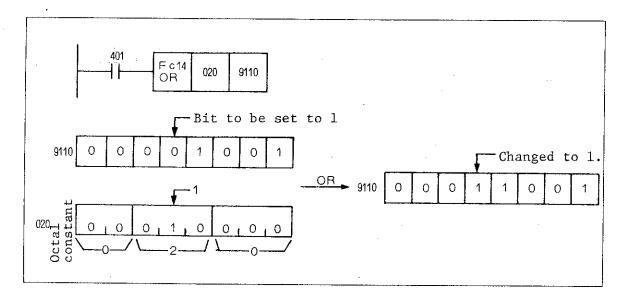

| [3]    | Bit insertion                                              |      |

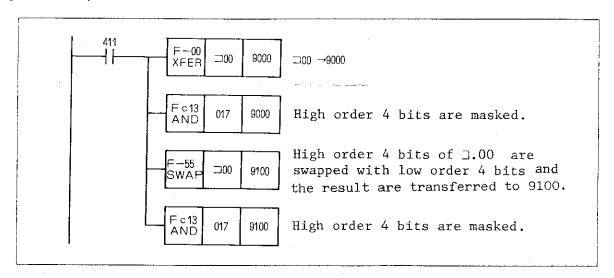

| [4]    | Decomposition of a number                                  |      |

| [5]    | Composition of a number                                    |      |

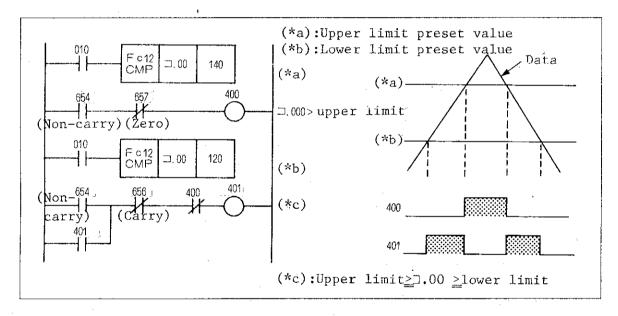

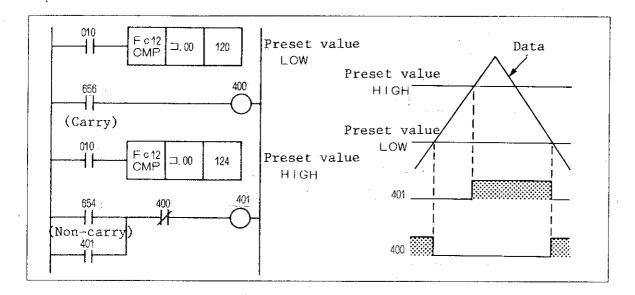

| [6]    | Comparison with preset value                               |      |

| [7]    | Window comparator                                          |      |

| [8]    | Comparator circuit having undetectable zone                | 227  |

|      |                                                       | Page |

|------|-------------------------------------------------------|------|

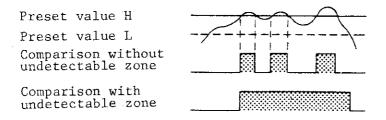

| [e]  | Timer that has multiple number of set points          | 228  |

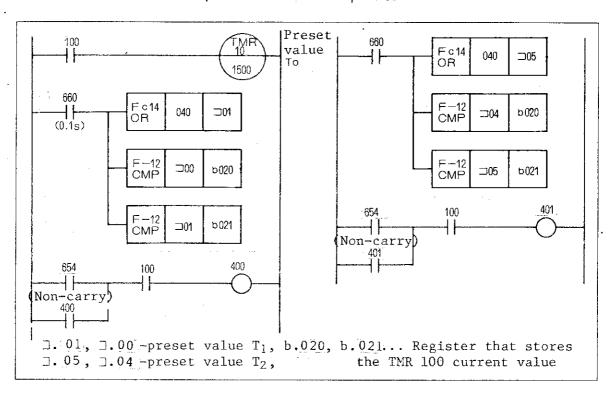

| [10] | Obtaining the result by the signed absolute value     | 229  |

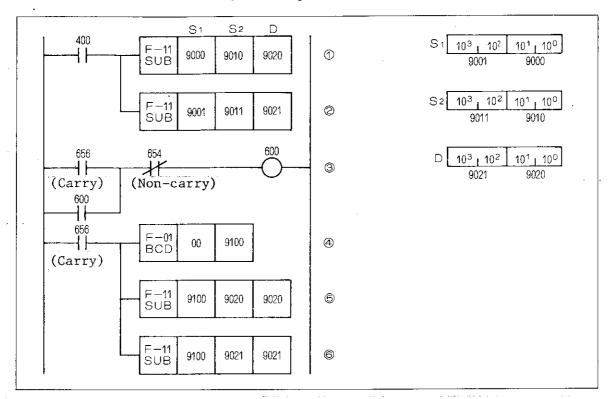

| [11] | Timer current value external output                   | 2,30 |

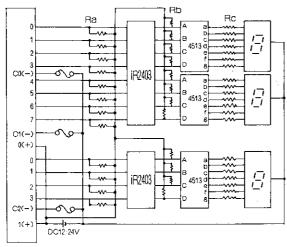

| [12] | Counter current value external output                 | 232  |

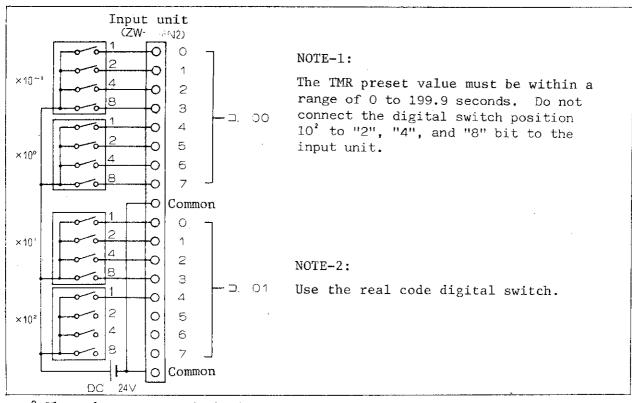

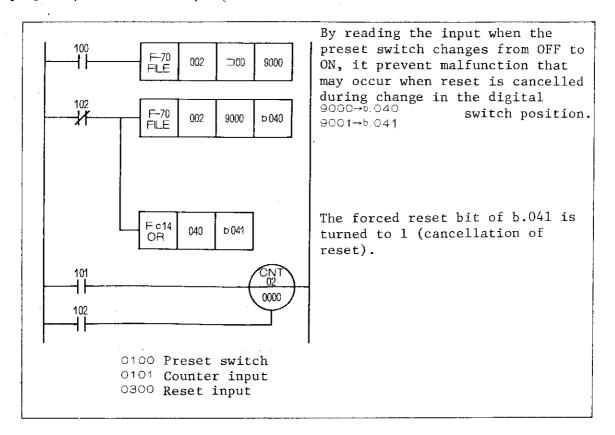

| [13] | Input of timer preset value from an external device   | 233  |

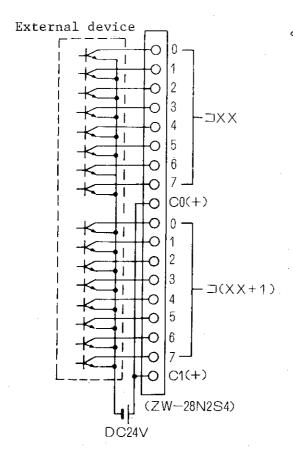

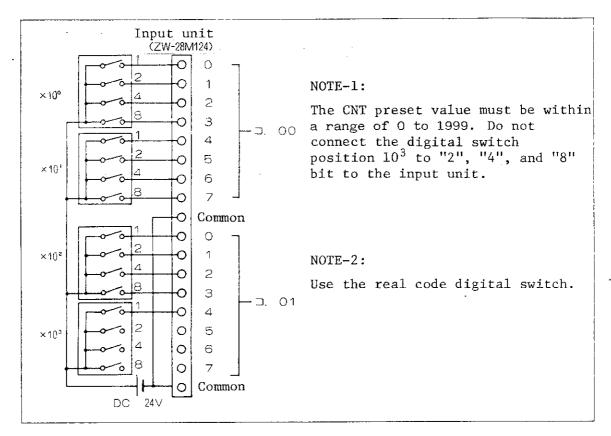

| [14] | Input of counter preset value from an external device | 235  |

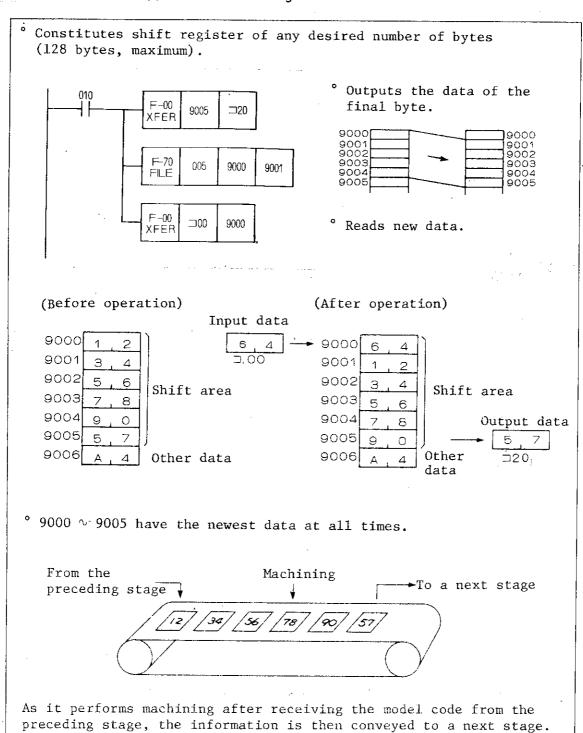

| [15] | Synchronous type FIFO stack register                  | 238  |

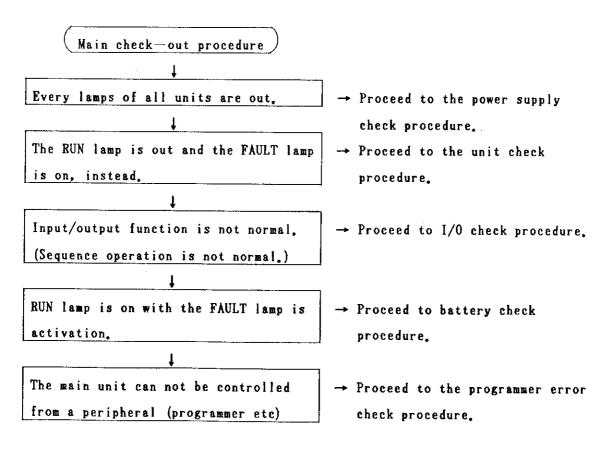

| 12   | Maintenance and Inspection                            | 239  |

| 12-  | -1 Routine maintenance                                | 239  |

| 1,2  | -2 Error check                                        | 241  |

## 9-2 Bit processing

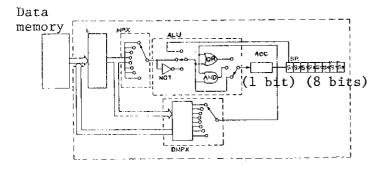

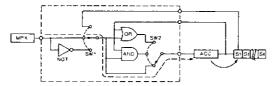

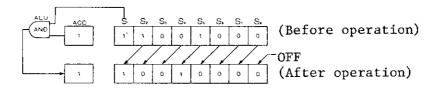

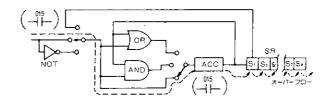

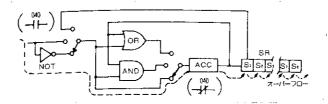

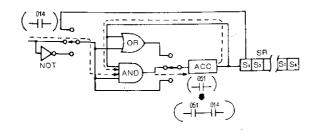

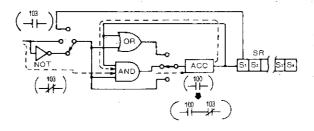

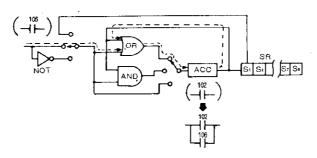

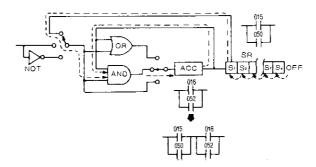

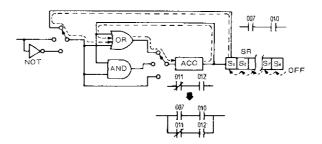

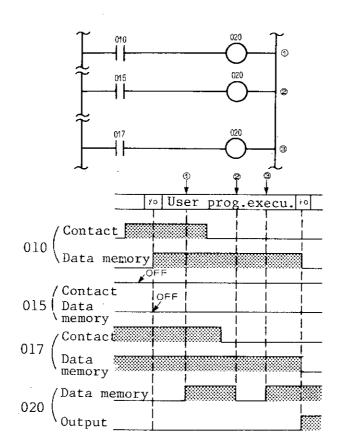

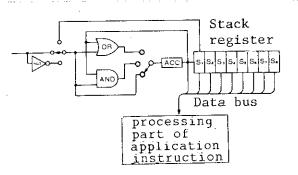

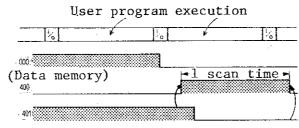

Bit processing means the logical operation of the contact signal which is carried out by the CPU with the WlO. See the block diagram next for bit operation by the CPU.

L (latch)

MPX (bit extraction)

ALU (single bit logical

unit)

ACC (accumulator)

SR (stack register)

DMPX (bit insertion)

#### (1) L (latch)

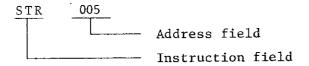

The bit processing instruction has the instruction field and the address field.

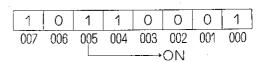

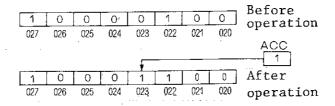

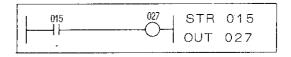

The address field represents the relay number of the data memory relay area (I/O relay, link relay, auxiliary relay, Retention relay). When the ON/OFF information of the relay is read from the data memory, the contents of one byte (8 bits) contained in that relay number are read and latched in the latch L. In the case of the instruction "STR 005", for instance, eight bits of 000  $^{\circ}$  007 are read.

#### (2) MPX (multiplexer)

The required one bit is extracted out of eight bits in the latch L. In the case of the instruction "STR 005", ON/OFF information of 005 is extracted out of 000  $\sim$  007.

#### (3) ALU (one bit logical unit)

Logical operation takes place according to the contents of the instruction field of the given instruction.

Figure above shows how the operation takes place for the STR instruction. The SW1 and SW2 is chosen according to the contents of the instruction field.

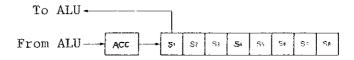

#### (4) ACC (accumulator)

A single bit register in which the result of the ALU is stored.

#### (5) SR (stack register)

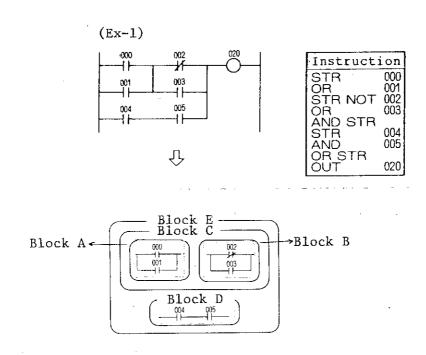

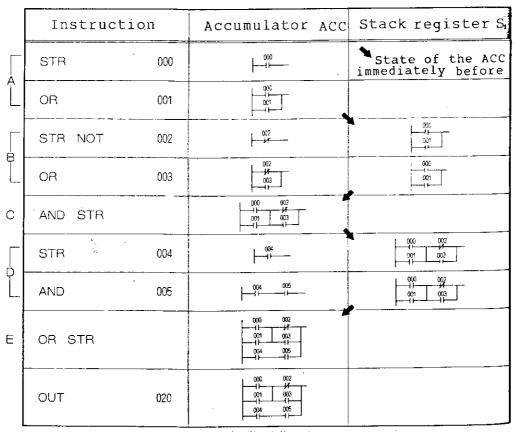

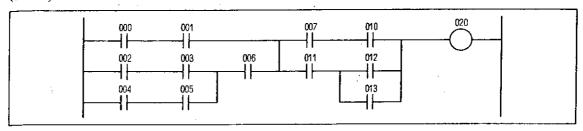

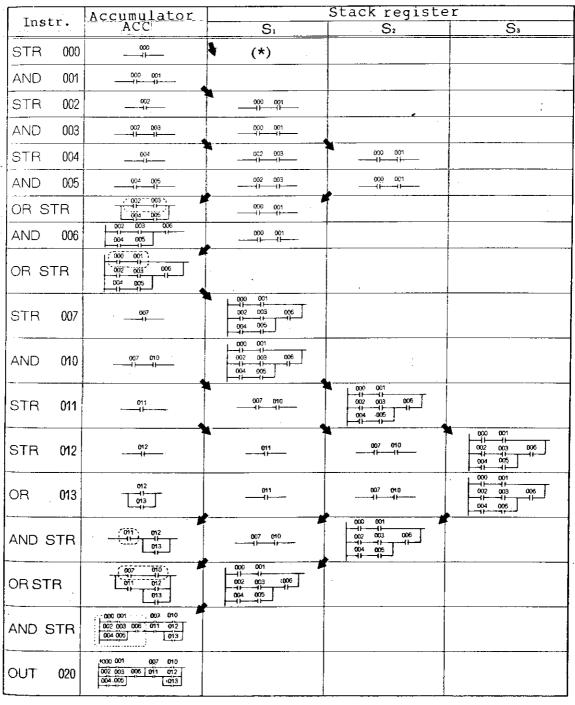

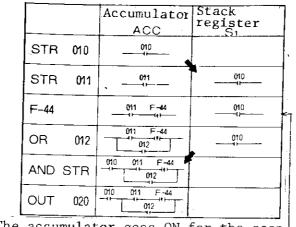

An 8-bit register in which the intermediate result is stored during processing of the serial/parallel circuit or application instruction that has plural number of input conditions.

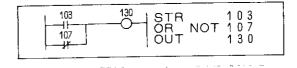

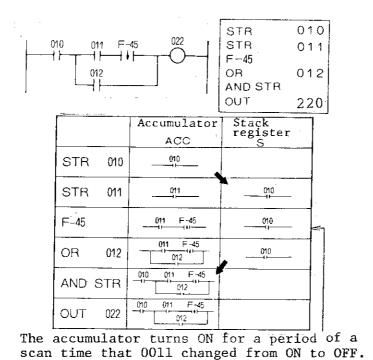

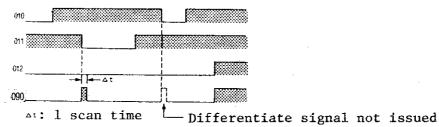

- 1 Shift register action during execution of the STR or STR NOT instruction

- ° With the STR and STR NOT instruction, the ON/OFF state of the one bit read from the data memory is stored in the accumulator. With the STR NOT instruction, the bit is inverted before being stored in the accumulator.

- ° The ON/OFF information previously stored in the accumulator shifts to  $S_1$ , the information in  $S_1$  to  $S_2$ , one in  $S_2$  to  $S_3$ , ...  $S_3$  to  $S_4$ ,  $S_4$  to  $S_5$ ,  $S_5$  to  $S_6$ ,  $S_6$  to  $S_7$ , and  $S_7$  to  $S_8$ . And the information in  $S_8$  is then erased.

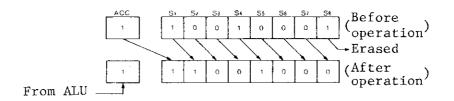

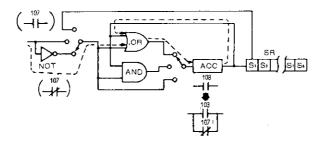

- ② Shift register action during execution of AND STR or OR STR instruction

- $^{\circ}$  With the AND STR and OR STR instruction, the ON/OFF information in  $S_1$  is stored in the ALU, to be ANDed or ORded with the accumulator contents, then the result is stored in the accumulator.

- ° The ON/OFF information of  $S_1$  which becomes unwanted after the operation is erased. The information in  $S_2$  shifts to  $S_1$ ,  $S_3$  to  $S_2$ ,  $S_4$  to  $S_3$ ,  $S_5$  to  $S_4$ ,  $S_6$  to  $S_5$ ,  $S_7$  to  $S_6$ ,  $S_8$  to  $S_7$ . And  $S_8$  is then set to OFF.

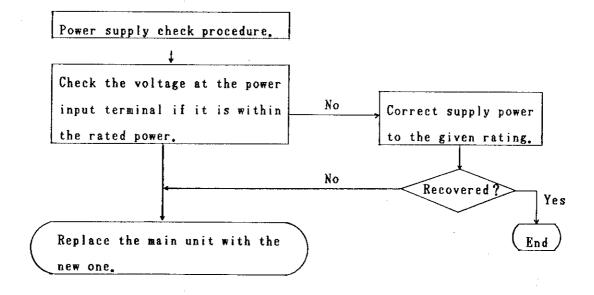

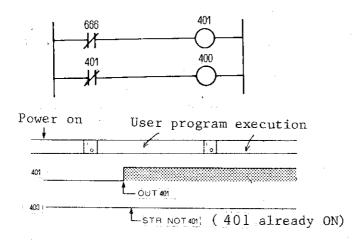

#### (6) DMPX (demultiplexer)